Floating point unit: design and implementation with portability

Unidad aritmética de punto flotante: diseño e implementación con portabilidad

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivatives 4.0 International License.

Copyright statement

The authors exclusively assign to the Universidad EIA, with the power to assign to third parties, all the exploitation rights that derive from the works that are accepted for publication in the Revista EIA, as well as in any product derived from it and, in in particular, those of reproduction, distribution, public communication (including interactive making available) and transformation (including adaptation, modification and, where appropriate, translation), for all types of exploitation (by way of example and not limitation : in paper, electronic, online, computer or audiovisual format, as well as in any other format, even for promotional or advertising purposes and / or for the production of derivative products), for a worldwide territorial scope and for the entire duration of the rights provided for in the current published text of the Intellectual Property Law. This assignment will be made by the authors without the right to any type of remuneration or compensation.

Consequently, the author may not publish or disseminate the works that are selected for publication in the Revista EIA, neither totally nor partially, nor authorize their publication to third parties, without the prior express authorization, requested and granted in writing, from the Univeridad EIA.

Show authors biography

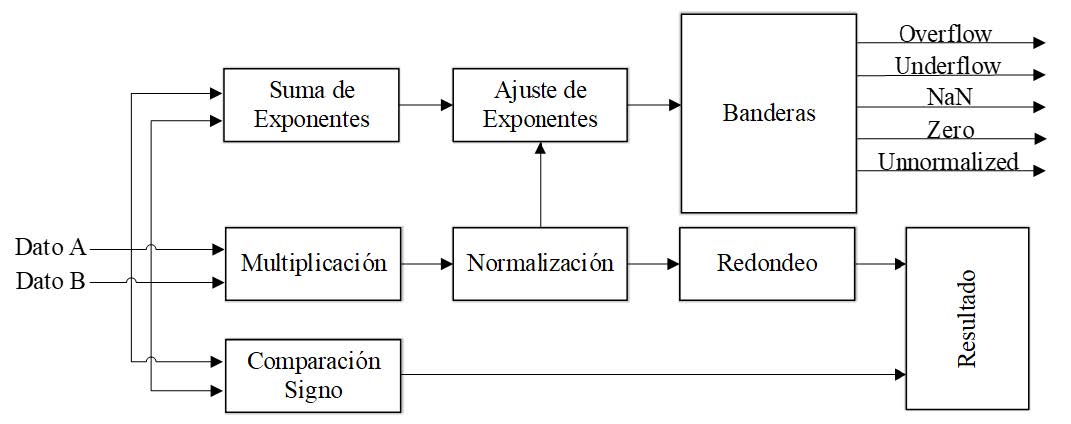

The use of floating point units (FPU) in digital processing has increased due to the high precision and range of numbers that can be represented. In image processing, digital filters with infinite impulse response (IIR), finite impulse response (FIR) and digital controllers these types of units are required to obtain more accurate results and avoid unstable responses, however, to implement these, some processors have built-in units, which implies a technological dependence on manufacturers to develop prototypes. To avoid this dependency, this article presents the design of the modules for the operations most used in digital signal processing: multiplication and addition / subtraction. The steps and considerations to take into account are presented, such as exceptions, rounding, and normalization of operands, in order to implement these operations in any Field Programmable Gate Arrays (FPGA). Results are checked using the MODELSIM® test bench and the error rate determined using MATLAB®.

Article visits 555 | PDF visits 417

Downloads

- Álvarez, J. A. y Lindig B., M. (2008) ‘Diseño de un Coprocesador Matemático de Precisión Simple usando el Spartan 3E’, Polibits, 38. Available at: https://www.redalyc.org/articulo.oa?id=402640451010.

- Barry, P. y Crowley, P. (2012) ‘Chapter 5 - Embedded Processor Architecture’, in Barry, P. and Crowley, P. B. T.-M. E. C. (eds). Boston: Morgan Kaufmann, pp. 99–152. doi: https://doi.org/10.1016/B978-0-12-391490-3.00005-9.

- BOLAÑOS, F. y BERNAL, Á. (2008) ‘Una implementación hardware optimizada para el operador exponenciación modular.’, Dyna, (156), pp. 55–63.

- Cantoro, R. et al. (2016) ‘In-field functional test programs development flow for embedded FPUs’, 2016 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems, DFT 2016, pp. 107–110. doi: 10.1109/DFT.2016.7684079.

- Cervantes, A. et al. (2016) ‘Implementation of an open core IEEE 754-based FPU with non-linear arithmetic support’, in 2016 IEEE 36th Central American and Panama Convention (CONCAPAN XXXVI), pp. 1–6. doi: 10.1109/CONCAPAN.2016.7942354.

- Chong, Y. J. y Parameswaran, S. (2011) ‘Configurable Multimode Embedded Floating-Point Units for FPGAs’, IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 19(11), pp. 2033–2044. doi: 10.1109/TVLSI.2010.2072996.

- Condia, J. E. R. et al. (2020) ‘Design and Verification of an open-source SFU model for GPGPUs’, in 2020 17th Biennial Baltic Electronics Conference (BEC), pp. 1–6. doi: 10.1109/BEC49624.2020.9276748.

- Guerrero-Balaguera, J.-D., Condia, J. E. R. y Reorda, M. S. (2021) ‘On the Functional Test of Special Function Units in GPUs’, in 2021 24th International Symposium on Design and Diagnostics of Electronic Circuits & Systems (DDECS), pp. 81–86. doi: 10.1109/DDECS52668.2021.9417025.

- Hamid, L. S. A. et al. (2010) ‘Design of Generic Floating Point Multiplier and Adder/Subtractor Units’, in 2010 12th International Conference on Computer Modelling and Simulation, pp. 615–618. doi: 10.1109/UKSIM.2010.117.

- José, W. et al. (2014) ‘Efficient implementation of a single-precision floating-point arithmetic unit on FPGA’, in 2014 24th International Conference on Field Programmable Logic and Applications (FPL), pp. 1–4. doi: 10.1109/FPL.2014.6927391.

- Joshi, M. N. y Gawali, D. H. (2016) ‘Floating point unit core for Signal Processing applications’, in 2016 Online International Conference on Green Engineering and Technologies (IC-GET), pp. 1–6. doi: 10.1109/GET.2016.7916650.

- Karlstrom, P., Ehliar, A. y Liu, D. (2008) ‘High-performance, low-latency field-programmable gate array-based floating-point adder and multiplier units in a Virtex 4’, IET Computers & Digital Techniques, 2(4), pp. 305–313. doi: 10.1049/iet-cdt:20070075.

- Kaur, P. et al. (2015) ‘Double Precision Floating Point Arithmetic Unit Implementation- A Review’, International Journal of Engineering Research & Technology (IJERT), 4(7), pp. 992–994. Available at: http: / /dx.doi.org/10.17577/IJERTV4IS070766.

- Lasith, K. K. y Thomas, A. (2014) ‘Efficient implementation of single precision floating point processor in FPGA’, in 2014 Annual International Conference on Emerging Research Areas: Magnetics, Machines and Drives (AICERA/iCMMD), pp. 1–5. doi: 10.1109/AICERA.2014.6908269.

- López, J., Restrepo, J. y Tobón, J. (2020) ‘Parametric Decimal Division using Hardware Description Language’, Revista EIA, 17, pp. 1–6. doi: https://doi.org/10.24050/reia.v17i33.1318.

- Malkapur, S. B. y Rajput, R. P. (2020) ‘Design of Generic Floating Point Pipeline Based Arithmetic Operation for DSP Processor’, in 2020 Second International Conference on Inventive Research in Computing Applications (ICIRCA), pp. 1059–1064. doi: 10.1109/ICIRCA48905.2020.9182948.

- Ramyarani, N. Subbiah, V. Deepa, P. (2019) ‘Design of area-efficient IIR filter using FPPE’, Turkish Journal of Electrical Engineering & Computer Sciences, 27(3), pp. 2321–2330. doi: :10.390.

- Russinoff, D. M. (2019) Formal Verification of Floating-Point Hardware Design. first edit. Austin, TX, USA: Springer. doi: 10.1007/978-3-319-95513-1.

- Sandoval-Ruiz, C. (2019) ‘Modelo VHDL de Control Neuronal sobre tecnología FPGA orientado a Aplicaciones Sostenibles ’, Ingeniare. Revista chilena de ingeniería . scielocl , pp. 383–395.

- STALLINGS, W. (2005) Organización y arquitectura de computadores. Séptima Ed. Madrid: PEARSON EDUCACIÓN.

- Veeranki, Y. R. and Nakkeeran, R. (2013) ‘Spartan 3E Synthesizable FPGA Based Floating-Point Arithmetic Unit’, International Journal of Computer Trends and Technology (IJCTT), 4, pp. 751–755. Available at: www.ijcttjournal.org.

- Wilton, C. Y. A. M. S. W. L. P. H. W. L. S. J. E. (2012) ‘Optimizing Floating Point Units in Hybrid FPGAs’, IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, 20(7), pp. 1295–1303. doi: 10.1109/TVLSI.2011.2153883.

- Zhang, B. y Zhao, J. (2017) ‘Elementary Function Computing Method for Floating-Point Unit’, Journal of Signal Processing Systems, 88(3), pp. 311–321. doi: 10.1007/s11265-016-1166-x.

- Zoni, D., Galimberti, A. y Fornaciari, W. (2021) ‘An FPU design template to optimize the accuracy-efficiency-area trade-off’, Sustainable Computing: Informatics and Systems, 29, p. 100450. doi: https://doi.org/10.1016/j.suscom.2020.100450.